实际运算放大器

背景

理想运算放大器:输入阻抗无穷大、开环增益无穷大、带宽无穷大、输入输出严格遵循过零点线性比例关系。在实际中很难直接买到

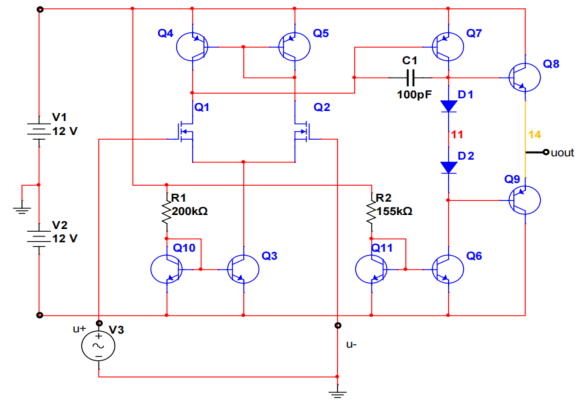

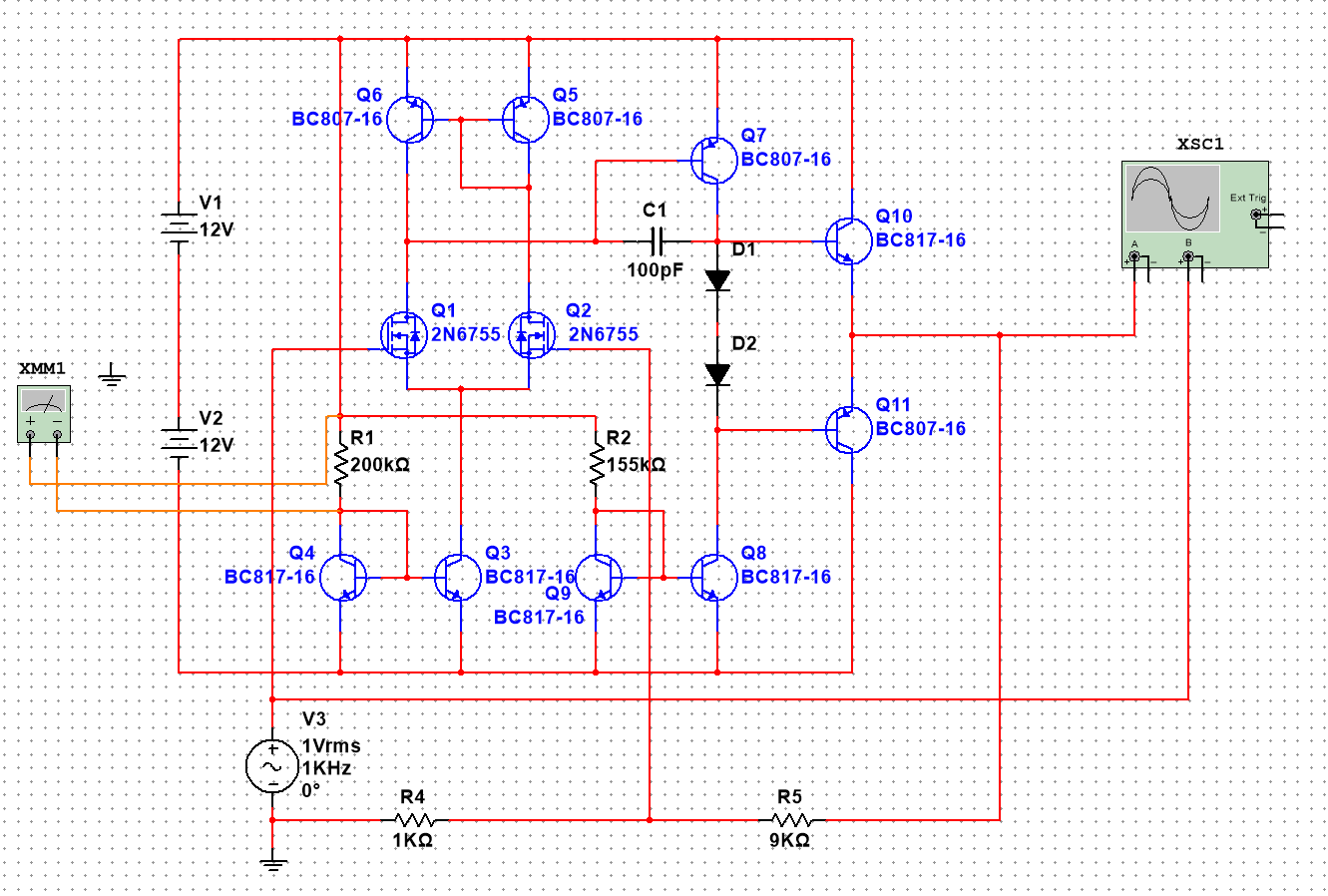

自制运算放大器

Q3,Q5,Q6:恒流源代替RC实现高增益放大(高动态电阻,低静态电阻)

C1:降低高频时的自激振荡

Q8,Q9:实现推挽输出,并且降低输出电阻

关键参数

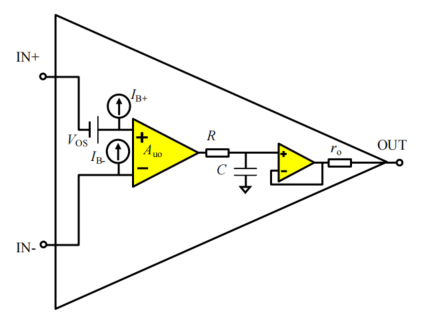

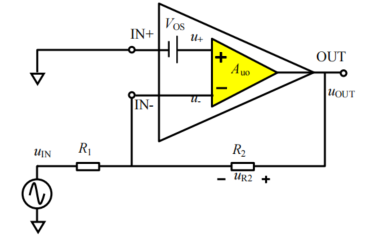

输入失调电压VOS: Input Offset Voltage

- 本质:当运放的两个输入端接地时,由于图中 VOS的存在,经过 Auo 倍放大,输出电压必然不是 0。在运放的负输入端施加一个可调节的直流电压 uOS,调节 uOS使得输出电压等于 0 时,此时的 uOS即为运放的输入失调电压 VOS。

- 根源:输入失调电压,是任何一个运放都存在的,它来自于运放内部电路的电路结构以及非对称性,是难以从根本上消除的

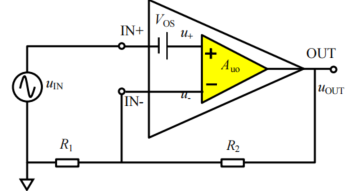

如上图所示的电路中,LM324设定失调电压为2mV,经过101倍放大,为200mV左右

分析失调电压的增益:

同相比例放大器

反向比例放大器

可以看到噪声增益都是一样的(都是从正端输入的-同相比例放大器)

输入偏置电流 IB:Input Bias Current

实际运放的两个输入端,在正常工作时,始终存在不为 0的静态流进电流

对 BJT 组成输入级的运放,这个电流就是差动输入级晶体管的基极电流 IBQ,没有它,差动输入级晶体管就没有合适的静态工作点,因此对 BJT 组成输入级的运放,此值是不小的。

对于场效应管组成输入级的运放,这个电流是输入级晶体管的门极静态漏电流,因此此值很小。

偏置电流主要受到温度、共模电压的影响。多数情况下,温度越高,偏置电流越大。共模电压是指实际工作时,两个输入端的共模电压,它对偏置电流的影响,随不同运放而不同,可以通过查阅数据手册获得。

输入失调电流 IOS:Input Offset Current

输入失调电流,是两个输入端静态电流的差值,一般没有正负区别

多数情况下,输入偏置电流与输入失调电流近似相等,或者维持在一个数量级。

决定输出失调电压大小的有三个因素:

独立的输入失调电压,

以及相互有关联的偏置电流和失调电流,而后面两个因素,又与外部电阻相关

降低上述三种情况的影响:

等效输入失调电压

对一个运放组成的放大电路,输出失调电压是由多种因素造成的,将输出失调电压除以电路总增益,即为等效输入失调电压。

输入电压范围:Input Voltage Range

保证运算放大器正常工作的最大输入电压范围,也称为共模输入电压范围。

优劣评定:一般运放的输入电压范围比电源电压范围窄 1V 到几 V,比如±15V 供电,输入电压范围在-12V~13V。较好的运放输入电压范围和电源电压范围相同,甚至超出范围0.1V。比如±15V 供电,输入范围在-15.1V 到 15.0V。当运放最大输入电压范围与电源范围比较接近时,比如相差 0.1V 甚至相等、超过,都可以叫“输入轨至轨”,表示为 Rail-to-rail input,或 RRI

理解:运放的两个输入端,任何一个的输入电压超过此范围,都将引起运放的失效。注意,超出此范围并不代表运放会被烧毁,但绝对参数中出现的此值是坚决不能超过的。

输出电压范围:VOH/VOL 或者 Swing from rail

定义:在给定电源电压和负载情况下,输出能够达到的最大电压范围。或者给出正向最大电压 VOH 以及负向最小电压 VOL——相对于给定的电源电压和负载;或者给出与电源轨(rail)的差距。

优劣范围:一般运放的输出电压范围要比电源电压范围略窄 1V 到几 V。较好的运放输出电压范围可以与电源电压范围非常接近,比如几十 mV 的差异,这被称为“输出至轨电压”。这在低电压供电场合非常有用。当厂家觉得这个运放的输出范围已经接近于电源电压范围时,就自称“输出轨至轨”,表示为 Rail-to-rail output,或 RRO

理解:在没有额外的储能元件情况下,运放的输出电压不可能超过电源电压范围,随着负载的加重,输出最大值与电源电压的差异会越大。

共模抑制比:Common-mode rejection ratio,CMRR

定义:运放的差模电压增益与共模电压增益的比值,可以用倍数表示,也可用 dB 表示。

优劣范围:一般运放都有 60dB 以上的 CMRR,高级的可达 140dB 以上。

共模抑制比,对减法器影响巨大

开环电压增益:Open-loop gain,AVO或者教科书常用的 Auo

定义:运放本身具备的输出电压与两个输入端差压的比值,一般用 dB 表示。理论上,它与输入信号频率相关,是一个随频率上升而下降的曲线。但在数据手册中,它一般用频率为 0Hz 处的值来表示。

优劣范围:一般在 60dB~160dB 之间。越大的,说明其放大能力越强。

理解:开环电压增益是指放大器在闭环工作时,实际输出除以运放正负输入端之间的压差,类似于运放开环工作——其实运放是不能开环工作的

压摆率:Slew rate,SR

定义:闭环放大器输出电压变化的最快速率。用 V/μs 表示。

优劣范围:从 2mV/μs 到 9000V/μs 不等。

理解:此值显示运放正常工作时,输出端所能提供的最大变化速率,当输出信号欲实现比这个速率还快的变化时,运放就不能提供了,导致输出波形变形——原本是正弦波就变成了三角波

单位增益带宽:Unity Gain-bandwidth,UGBW

定义:运放开环增益-频率图中,开环增益下降到 1 时的频率。

优劣范围:从 10kHz 到 1GHz,差别很大。一般来讲,超过 50MHz 属于宽带放大器。

理解:当输入信号频率高于此值时,运放的开环增益会小于 1,即此时放大器不再具备放大能力。这是衡量运放带宽的一个主要参数。

增益带宽积:Gain Bandwidth Product,GBP 或者 GBW

定义:运放开环增益-频率图中,指定频率处,开环增益与该指定频率的乘积。

理解:如果运放开环增益始终满足-20dB/10 倍频的规律,也就是频率提高 10 倍,开环增益变为原先的 0.1 倍,那么它们的乘积将是一个常数,也就等于前述的“单位增益带宽”,或者“1Hz 处的增益”。

-3dB 带宽

定义:运放闭环使用时,某个指定闭环增益(一般为 1 或者 2、10 等)下,增益变为低频增益的 0.707 倍时的频率。分为小信号(输出 200mV 以下)大信号(输出 2V)两种。

理解:它直接指出了使用该运放可以做到的闭环放大电路的-3dB 带宽。因为前述的两个参数,单位增益带宽和增益带宽积,其实都是对运放开环增益性能的一种描述,来自开环增益/频率图。而这个参数是对运放接成某种增益的放大电路实施实测得到的。

满功率带宽:Full Power Bandwidth

定义:将运放接成指定增益闭环电路(一般为 1 倍),连接指定负载,输入端加载正弦波,输出为指标规定的最大输出幅度,此状态下,不断增大输入信号频率,直到输出出现因压摆率限制产生的失真(变形)为止,此频率即为满功率带宽。

理解:比-3dB 带宽更为苛刻的一个限制频率。它指出在此频率之内,不但输出幅度不会降低,且能实现满幅度的大信号带载输出。

至稳时间:Settling Time

定义:运放接成指定增益(一般为 1),从输入阶跃信号开始,到输出完全进入指定误差范围所需要的时间。所谓的指定误差范围,一般有 1%,0.1%几种。

优劣范围:几个 ns 到几个 ms。

理解:至稳时间由三部分组成,第一是运放的延迟,第二是压摆率带来的爬坡时间,第三是稳定时间。很显然,这个参数与 SR 密切相关,一般来说,SR 越大的,至稳时间更小

相位裕度 Phase margin,𝝋𝒎和增益裕度

相位裕度定义:在运放开环增益和开环相移图中,当运放的开环增益下降到 1 时,开环相移值减去-180°得到的数值。

增益裕度定义:在运放开环增益和开环相移图中,当运放的开环相移下降到-180°时,增益 dB 值取负,或者是增益值的倒数。

理解:相位裕度和增益裕度越大,说明放大器越容易稳定

电源电压抑制比

理论上,当电源电压发生改变时,运放构成的放大电路输出不应该变化。但是实际却会变化——放大电路的噪声增益 GN 越大,由此带来的输出的变化量也越大。

电源电压抑制比,其含义是运放对电源上纹波或者噪声的抵抗能力。首先,正负电源具有不一定相同的 PSRR,其次,随着电源电压变化频率的提升,运放对这个变化的抵抗能力会下降。一般情况下,电源变化频率接近其带宽时,运放会失去对电源变化的抵抗——即单位增益情况下电源变化多少,输出就变化多少。

频率越高,运放对电源纹波或者噪声的抵抗能力越弱。旁路电容的作用就是滤除电源上的噪声或者波动,特别在高频处,更需要滤除。

热阻

热阻标准定义:是导热体阻止热量散失程度的描述,以 1W 发热源在导热路径两端形成的温度差表示,单位为℃/W。有以下常用的两种:

θJA,是指芯片热源结(Junction)与芯片周围环境(Ambient)(一般为空气)的热阻。

θJC,是指芯片热源结(Junction)与芯片管壳(Case)的热阻。

理解:对芯片来说,导热路径的两端分别为自身发热体与环境空气。热阻 θJA 越大,说明散热越困难,其温差也就越大